source: | ||

| Definition of Metastability : | |

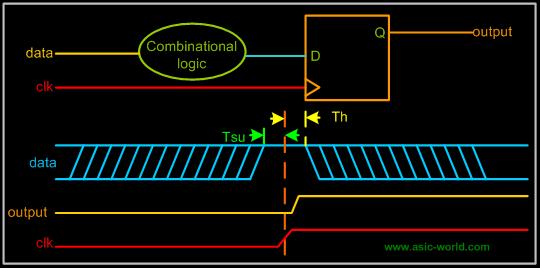

Whenever there are setup and hold time violations in any flip-flop, it enters a state where its output is unpredictable: this state is known as metastable state (quasi stable state); at the end of metastable state, the flip-flop settles down to either '1' or '0'. This whole process is known as metastability. In the figure below Tsu is the setup time and Th is the hold time. Whenever the input signal D does not meet the Tsu and Th of the given D flip-flop, metastability occurs. | ||

| ||

| ||

| ||

When a flip-flop is in metastable state, its output oscillate between '0' and '1' as shown in the figure below (here the flip-flop output settles down to '0') . How long it takes to settle down, depends on the technology of the flip-flop. | ||

| ||

|

| ||

| | If we look deep inside of the flip-flop we see that the quasi-stable state is reached when the flip-flop setup and hold times are violated. Assuming the use of a positive edge triggered "D" type flip-flop, when the rising edge of the flip-flop clock occurs at a point in time when the D input to the flip-flop is causing its master latch to transition, the flip-flop is highly likely to end up in a quasi-stable state. This rising clock causes the master latch to try to capture its current value while the slave latch is opened allowing the Q output to follow the "latched" value of the master. The most perfectly "caught" quasi-stable state (on the very top of the hill) results in the longest time required for the flip-flop to resolve itself to one of the stable states. | |

| ||

| ||

| ||

| How long does it stay in this state? | |

The relative stability of states shown in the figure above shows that the logic 0 and logic 1 states (being at the base of the hill) are much more stable than the somewhat stable state at the top of the hill. In theory, a flip-flop in this quasi-stable hilltop state could remain there indefinitely but in reality it won't. Just as the slightest air current would eventually cause a ball on the illustrated hill to roll down one side or the other, thermal and induced noise will jostle the state of the flip-flop causing it to move from the quasi-stable state into either the logic 0 or logic 1 state. | ||

| ||

| ||

| What are the cases in which metastability occurs? | |

| As we have seen that whenever setup and hold violation time occurs, metastability occurs, so we have to see when signals violate this timing requirement: | ||

| ||

| ||

| ||

| What is MTBF? | |

MTBF is Mean time between failure, what does that mean? Well MTBF gives us information on how often a particular element will fail or in other words, it gives the average time interval between two successive failures. The figure below shows a typical MTBF of a flip-flop and also it gives the MTBF equation. I am not looking here to derive MTBF equation :-) | ||

| ||

| ||

| | ||

| | ||

| | ||

| | ||

| | ||

| | ||

| | ||

Normally, | ||

|

| ||

| |

| |

| ||

| METASTABILITY REFERENCES | |

| ||

|

Monday, January 2, 2012

Definition of Metastability...

Subscribe to:

Post Comments (Atom)

No comments:

Post a Comment